Prova di esonero (28 giugno 2002)

| Cognome e nome _ |  |

|------------------|--|

| Matricola        |  |

L'interfaccia IFMAX riceve in continuazione da un bus esterno EXTDATA  $_{0-15}$  dati numerici paralleli a 16 bit in complemento a 2, sincronizzati a un clock esterno EXTCLK con frequenza 1 MHz. Su comando dalla CPU PD32, IFMAX esamina un blocco di 256 dati consecutivi, calcola il massimo  $V_{\rm max}$  dei valori presenti nel blocco, e trasmette il risultato alla CPU. A sua volta, la CPU mantiene in una variabile VMINMAX il minimo dei valori  $V_{\rm max}$  ricevuti.

Progettare l'interfaccia IFMAX e codificare il relativo software di pilotaggio.

### Calcolatori Elettronici II (A-L) Sessione estiva – Appello del 9 luglio 2002

| Cognome e nome |  |  |

|----------------|--|--|

| Matricola      |  |  |

#### Prima prova (15 punti)

Un'interfaccia IFRANGE è connessa a un bus esterno EXTDATA  $_{0-15}$  su cui transitano dati numerici paralleli sincronizzati a un clock esterno EXTCLK. IFRANGE riceve dalla CPU PD32 due valori numerici  $V_{\min}$  e  $V_{\max}$ , quindi avvia l'acquisizione di una sequenza di 1024 dati EXTDATA, determina il numero N di valori della sequenza compresi nell'intervallo [ $V_{\min}$ ,  $V_{\max}$ ], e trasmette tale risultato alla CPU. Quest'ultima confronta il valore ricevuto di N con un valore di soglia  $N_0$  e:

- decrementa  $V_{\min}$  e incrementa  $V_{\max}$  se  $N < N_0$

- incrementa  $V_{\min}$  e decrementa  $V_{\max}$  se  $N > N_0$

dopo di che riavvia il processo.

Progettare l'interfaccia IFRANGE e codificare il relativo software di pilotaggio.

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Martedì 16 luglio 2002, ore 09:00 (Aula 14, Via Scarpa)

### Calcolatori Elettronici II (A-L) Sessione estiva – Appello del 23 luglio 2002

| Cognome e nome |  | <br> |

|----------------|--|------|

| Matricola      |  |      |

### Prima prova (15 punti)

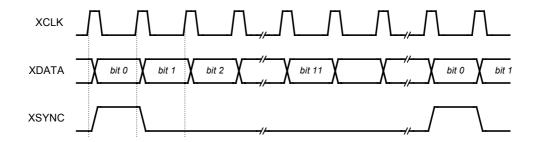

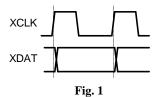

Un'interfaccia SERIN riceve in continuazione dal mondo esterno parole a 12 bit su una linea seriale XDATA, sincronizzate a un clock XCLK e a un segnale XSYNC:

dove il bit 0 è il bit meno significativo della parola. SERIN assembla i dati ricevuti e li invia in formato parallelo alla CPU PD32, che li dispone in un buffer circolare da 1024 word allocato all'indirizzo 7000000h.

Progettare l'interfaccia SERIN e codificare il relativo software di pilotaggio.

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Venerdì 26 luglio 2002, ore 09:00 (Aula 11, Via Scarpa)

Sessione estiva – Appello del 9 settembre 2002

| Cognome e nome |  |

|----------------|--|

| Matricola      |  |

### Prima prova (15 punti)

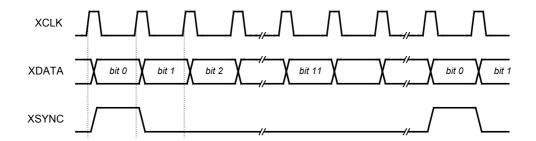

Una CPU PD32 preleva dati a 12 bit da un buffer circolare da 2048 word e li trasmette ad una interfaccia SEROUT, che li serializza su una linea **XDATA** sincronizzandoli a un clock **XCLK**, generato internamente all'interfaccia; il bit meno significativo (bit 0) di ciascuna parola da 12 bit viene emesso per primo, ed è identificato da un segnale **XSYNC**, anch'esso generato da SEROUT:

Le linee XDATA, XCLK, XSYNC vengono poi inviate al mondo esterno.

Progettare l'interfaccia SEROUT e codificare il relativo software di pilotaggio.

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Lunedì 16 settembre 2002, ore 09:00, Aula 11 (Via Scarpa).

Appello del 13 dicembre 2002

| Cognome e nome |  |

|----------------|--|

| Matricola      |  |

### Prima prova (15 punti)

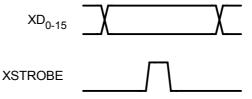

Una periferica IFPTY acquisisce dati paralleli da 16 linee  $XD_{0-15}$ , sincronizzati ad un segnale esterno XSTROBE:

IFPTY verifica la parità di ciascun dato (ossia che il numero dei bit uguali ad 1 sia pari) e, se il dato è corretto, lo invia alla CPU PD-32, la quale lo accoda in un buffer da 4096 word. Al completamento del buffer, la CPU legge da IFPTY il numero di errori riscontrati, dopo di che avvia un nuovo ciclo di acquisizione.

Progettare l'interfaccia IFPTY e codificare il relativo software di pilotaggio.

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Martedì 17 dicembre 2002, ore 11:00, Aula 11 (Via Scarpa).

Esonero del 19 giugno 2003

| Cognome e nome |  |

|----------------|--|

| Matricola      |  |

#### Prova unica (15 punti)

Un'interfaccia IFTEMP acquisisce misure di temperatura da 16 sensori termici e controlla l'accensione e lo spegnimento di altrettanti elementi riscaldanti; i dati di temperatura sono espressi come valori da 8 bit in complemento a 2. L'interfaccia contiene inoltre un timer da 5 secondi, asservito al clock della CPU PD-32 che ha frequenza 100 MHz.

Ogni 5 secondi la CPU esegue un ciclo completo di acquisizione e controllo, che consiste nel confrontare la temperatura  $T_i$  misurata dall'i-esimo sensore ( $0 \le i < 16$ ) con due valori di soglia residenti in memoria  $M_i$ ,  $N_i$  (dove  $M_i < N_i$ ) e nel controllare lo stato dell'i-esimo elemento riscaldante secondo le regole seguenti:

- se  $T_i > N_i$ , l'i-esimo elemento riscaldante viene spento;

- se  $T_i < M_i$ , l'i-esimo elemento riscaldante viene acceso;

- altrimenti, lo stato dell'*i*-esimo elemento riscaldante rimane invariato.

Si progetti l'hardware dell'interfaccia e si codifichi il relativo software di gestione.

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

Appello del 7 luglio 2003

| Cognome e nome |  |

|----------------|--|

| Matricola      |  |

#### Prima prova (15 punti)

Un'interfaccia IFRTC (Real Time Clock) utilizza un generatore interno di clock a 32 kHz per mantenere un orologio in tempo reale con le seguenti informazioni: anno, mese, giorno, ore, minuti, secondi, millisecondi.

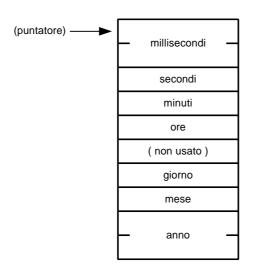

Il driver software residente sulla CPU PD-32 è strutturato in due subroutine, GET\_RTC e SET\_RTC, ciascuna delle quali accetta come argomento un puntatore a un blocco di dati da 10 byte così strutturato:

La subroutine GET\_RTC legge dall'interfaccia le informazioni di data/ora corrente e riempie il blocco, mentre la subroutine SET\_RTC utilizza le informazioni trovate nel blocco per inizializzare l'orologio.

Descrivere la struttura hardware dell'interfaccia IFRTC (assumendo che gli anni esattamente divisibili per 4 siano *sempre* bisestili) e codificare le due subroutine di pilotaggio.

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Venerdì 11 luglio 2003, ore 09:00, Aula 5 (Via del Castro Laurenziano).

Appello del 21 luglio 2003

| Cognome e nome |  |

|----------------|--|

| Matricola      |  |

#### Prima prova (15 punti)

Una periferica IFKEY contiene una memoria a sola lettura (ROM) organizzata in 2<sup>20</sup> parole da 56 bit, dove ogni parola è suddivisa in un campo *chiave* (**KEY**) da 24 bit e un campo *informazione* (**INFO**) da 32 bit; le parole nella ROM sono ordinate per valori crescenti di **KEY**. La periferica riceve dalla CPU PD-32 un valore **KEY** ed esegue una ricerca nella ROM; se tale chiave viene trovata, restituisce alla CPU il corrispondente valore del campo **INFO**, altrimenti restituisce **00000000h**.

Progettare l'hardware della periferica, e codificare una subroutine che gestisce la ricerca attraverso IFKEY e riceve come argomenti:

- un puntatore a una tavola **KEYTABLE** contenente un elenco di chiavi per ciascuna delle quali eseguire la ricerca;

- il numero di elementi della tavola suddetta;

- un puntatore a una tavola **INFOTABLE** nella quale la stessa subroutine dispone ordinatamente le informazioni restituite dalla periferica per ciascuna chiave presente in **KEYTABLE**.

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Venerdì 25 luglio 2003, ore 09:00, Aula 5 (Via del Castro Laurenziano).

Appello del 10 settembre 2003

| Cognome e nome |  |

|----------------|--|

| Matricola      |  |

#### Prima prova (15 punti)

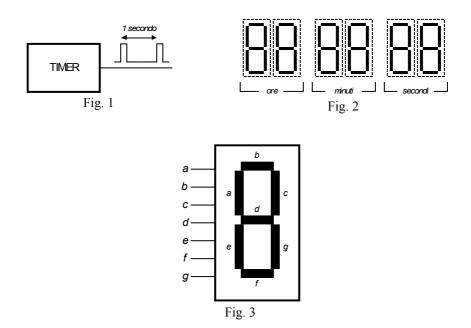

Una periferica IFCLK, dedicata alla visualizzazione dell'ora corrente, contiene un modulo Timer (Fig. 1) mediante il quale essa invia interruzioni alla CPU PD-32 con cadenza di uno al secondo. In risposta all'interrupt, la CPU mantiene <u>in memoria</u> il conteggio dell'ora corrente, espresso in ore/minuti/secondi, e lo presenta su un dispositivo di visualizzazione (Fig. 2) residente sulla periferica stessa. Tale dispositivo è a sua volta costituito da 6 *display a sette segmenti*, ciascuno dei quali (Fig. 3) è utilizzato per la visualizzazione di una singola cifra decimale ed è dotato di 7 ingressi digitali che controllano direttamente l'accensione o lo spegnimento dei rispettivi segmenti.

Progettare l'hardware della periferica IFCLK, e codificare il software per l'aggiornamento e la presentazione delle informazioni di ore/minuti/secondi.

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

Tempo a disposizione: 2 ore.

Discussione e verbalizzazione: Venerdì 12 settembre 2003, ore 09:00, Aula 6 (Via del Castro Laurenziano).

Appello del 9 dicembre 2003

| Cognome e nome |  |

|----------------|--|

| Matricola      |  |

#### Prima prova (15 punti)

Progettare un DMA Controller per il trasferimento di dati dalla memoria del PD-32 verso il mondo esterno in modo che la CPU abbia la possibilità di definire, con l'invio di opportuni comandi al Controller stesso:

- l'ampiezza delle parole trasferite: byte, word, oppure doubleword;

- il **verso di scansione** dell'area di memoria interessata: per indirizzi crescenti, oppure decrescenti;

- la modalità di trasferimento: a burst oppure in cycle stealing.

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Lunedì 15 dicembre 2003, ore 09:00, Aula 2 Giovedì 11 dicembre 2003, ore 09:00, Aula 5 (Via del Castro Laurenziano).

Esonero dell'8 giugno 2004

| Cognome e nome |  |

|----------------|--|

| Matricola      |  |

### Prova unica (15 punti)

Una periferica IFPER riceve un segnale esterno XSIG avente periodo variabile da 0.5 a 4 microsec, ed esegue misure di periodo su tale segnale utilizzando il System Clock a 200 MHz come base dei tempi.

Progettare l'hardware della periferica e codificare una subroutine di pilotaggio mediante cui la CPU PD-32 acquisisce 16 misurazioni consecutive  $p_0, p_1, ..., p_{15}$  dalle quali calcola

• la media delle misure:

$$M = \frac{1}{16} \sum_{i=0}^{15} p_i$$

• la media dei valori assoluti degli scarti:

$$S = \frac{1}{16} \sum_{i=0}^{15} |p_i - M|$$

Il sottoscritto, ai sensi della legge 675 del 31/12/96, autorizza il docente a pubblicare su web i risultati della presente prova.

Firma leggibile

.....

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

### Calcolatori Elettronici II (M-Z) Appello del 28 giugno 2004

| Cognome e nome |  |

|----------------|--|

| Matricola      |  |

### Prima prova (15 punti)

Una periferica IFSTR riceve dall'esterno dati seriali attraverso una linea XDATA e un clock XCLK. La CPU PD-32, dopo aver inviato alla periferica un numero N < 4096 e un dato a 12 bit  $S = s_{11}s_{10}...s_1s_0$ , attiva l'acquisizione di una stringa binaria T costituita da N bit consecutivi prelevati dalla linea XDATA. Al termine dell'acquisizione, IFSTR comunica alla CPU:

- il numero A di sottostringhe  $S = s_{11}s_{10}...s_1s_0$  trovate all'interno della stringa T;

- il numero *B* di sottostringhe  $S' = s_0 s_1 ... s_{10} s_{11}$  trovate all'interno della stringa *T*.

Progettare l'hardware della periferica IFSTR e codificare il software di controllo sotto forma di subroutine che accetta in ingresso il puntatore ad una tavola residente in memoria e organizzata come segue:

| NPTR |

|------|

| SPTR |

| APTR |

| BPTR |

#### dove

- NPTR e SPTR sono i puntatori alle locazioni che contengono il numero *N* e il dato *S* da trasmettere a IFSTR;

- APTR e BPTR sono i puntatori alle locazioni dove andranno immagazzinati i numeri *A* e *B* ottenuti da IFSTR.

Il sottoscritto, ai sensi della legge 675 del 31/12/96, autorizza il docente a pubblicare su web i risultati della presente prova.

| Firma leggibile |  |

|-----------------|--|

|                 |  |

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Venerdì 2 luglio 2004, ore 09:00, Aula 4 (Via del Castro Laurenziano).

#### Calcolatori Elettronici II (M-Z) Appello del 9 luglio 2004

| Cognome: |            | Nome: |  |

|----------|------------|-------|--|

|          | Matricola: |       |  |

#### Prima prova (15 punti)

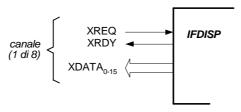

Una periferica IFDISP è connessa a 8 canali di comunicazione, ciascuno dei quali è costituito da 16 linee dati in uscita e due segnali di handshake (Fig. 1).

Fig. 1

All'arrivo di una richiesta di servizio XREQ da parte di un qualsiasi canale (Fig. 2):

- la periferica segnala l'evento alla CPU PD-32;

- il software di pilotaggio di IFDISP estrae un dato a 16 bit da una coda circolare da 4Kbyte residente in memoria e lo consegna alla periferica;

- la periferica trasmette il dato alle linee XDATA del canale che ne aveva fatto richiesta, e attiva nel contempo la linea XRDY dello stesso canale (Fig. 2) notificando in tal modo il completamento del servizio.

Progettare l'hardware della periferica e codificare il relativo software di pilotaggio, corredandolo di adeguati commenti.

Ai sensi della legge n. 675 del 31/12/96, il/la sottoscritto/a autorizza la pubblicazione su web dei risultati della presente prova.

Firma leggibile

.....

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

Discussione e verbalizzazione: Martedì 13 luglio 2004, ore 09:00, Aula 1 (Via del Castro Laurenziano).

### Calcolatori Elettronici II (M-Z) Appello del 13 settembre 2004

| Cognome: |            | . Nome: |  |

|----------|------------|---------|--|

|          | Matricola: |         |  |

#### Prima prova (15 punti)

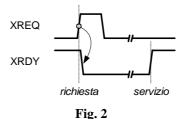

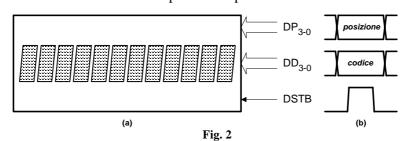

Una periferica IFBCD (Fig. 1) riceve dati a 4 bit dalle linee  $XIN_{0-3}$  sincronizzati a un clock XCLK. Un *messaggio* su tali linee è costituito dalla sequenza di dati:

- 1111 (intestazione del messaggio)

- **0xxx** (interpretato come un numero k,  $0 \le k < 8$ )

- da una a quattro cifre BCD (Binary Coded Decimal)

- 1110 (termine del messaggio)

Per ogni messaggio ricevuto, la periferica converte le cifre BCD ricevute in un numero binario N a 16 bit (la prima cifra BCD ricevuta è la più significativa, si veda l'esempio in Fig. 2) e invia il risultato al canale di uscita  $\texttt{XOUT}k_{0-15}$  identificato dal numero k contenuto nel messaggio.

Inoltre, il numero k e il numero N vengono inviati alla CPU PD-32, la quale aggiorna una tavola, residente in memoria, in cui per ciascun canale di uscita XOUT vengono mantenuti il minimo e il massimo dei numeri N ad esso inviati.

Fig. 1

Progettare l'hardware della periferica e codificare il relativo software di pilotaggio, corredandolo di adeguati commenti.

Ai sensi della legge n. 675 del 31/12/96, il/la sottoscritto/a autorizza la pubblicazione su web dei risultati della presente prova.

Firma leggibile

.....

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Martedì 21 settembre 2004, ore 09:00, Aula 2 (Via del Castro Laurenziano).

### Calcolatori Elettronici II (M-Z) Appello del 17 dicembre 2004

| Cognome: |            | Nome: |  |

|----------|------------|-------|--|

|          | Matricola: |       |  |

### Prima prova (15 punti)

Una periferica IFSPK per CPU PD-32 produce messaggi audio sintetizzati verso un canale di uscita costituito da 8 linee di output  $XD_{0-7}$  e da un clock esterno XCLK da 8 kHz. Un *messaggio* è costituito da una sequenza di campioni audio da 8 bit, che vengono applicati alle linee  $XD_{0-7}$  e sincronizzati con XCLK. Una memoria ROM, residente sulla periferica e organizzata in 16M parole da 8 bit, contiene i campioni relativi a 256 messaggi, nessuno dei quali ha durata di emissione superiore ai 10 secondi.

La subroutine di controllo di IFSPK accetta in ingresso un numero N ( $0 \le N < 256$ ) che identifica un messaggio da emettere, e che viene utilizzato come indice in una tavola residente nella memoria del sistema; ogni elemento della tavola contiene l'indirizzo iniziale del messaggio corrispondente nella ROM e il numero di campioni da cui esso è costituito. La subroutine comanda quindi la selezione del messaggio sulla periferica e l'emissione del messaggio stesso, e ritorna al chiamante solo ad emissione completata.

Progettare l'hardware della periferica e codificare il relativo software di pilotaggio, corredandolo di adeguati commenti.

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Martedì 21 dicembre 2004, ore 08:00, Aula 14 (Via Scarpa).

#### Calcolatori Elettronici II (A-L) Appello del 6 luglio 2005

| Cognome: |            | <i>Nome:</i> | <br> |

|----------|------------|--------------|------|

|          | Matricola: |              |      |

#### Prima prova (15 punti)

Un'interfaccia IFABS riceve in continuazione da un bus externo XDATA<sub>0-15</sub> dati numerici paralleli a 16 bit in complemento a 2, sincronizzati a un clock esterno XCLK. Su comando della CPU, IFABS procede all'acquisizione di un blocco da 1024 dati, dei quali calcola il massimo e il minimo dei valori assoluti:

$$A = \max_{i} |x_{i}| \qquad B = \min_{i} |x_{i}|$$

Questi due risultati vengono quindi trasmessi alla CPU che calcola il valore

$$U = \frac{A+B}{2}$$

e aggiorna le seguenti locazioni di memoria:

- AMIN con il minimo tra tutti i valori *A* acquisiti;

- BMAX con il massimo tra tutti i valori *B* acquisiti;

- UMIN e UMAX col minimo e, rispettivamente, il massimo tra tutti i valori *U* calcolati.

Progettare l'hardware della periferica e codificare il relativo software di pilotaggio, corredandolo di adeguati commenti.

| Firma leggibile |  |

|-----------------|--|

| <br>            |  |

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

Discussione e verbalizzazione: Lunedì 11 luglio 2005, ore 09:00, Aula 5 (Via del Castro Laurenziano).

#### Calcolatori Elettronici II (A-L) Appello del 20 luglio 2005

| Cognome: |              | Nome: |  |

|----------|--------------|-------|--|

|          | Matricola: . |       |  |

#### Prima prova (15 punti)

Un'interfaccia IFGCD, che opera come coprocessore per il calcolo del massimo comun divisore (*greatest commmon divisor*, GCD), riceve dalla CPU PD-32 una coppia (X,Y) di numeri interi assoluti a 32 bit e calcola Z = GCD(X,Y) secondo l'*algoritmo di Euclide*, dove X e Y sono entrambi non nulli e REM(X,Y) rappresenta il resto della divisione intera di X per Y:

- (1) Si determina R = REM(X,Y).

- (2) Se R = 0, l'algoritmo termina con Z = Y come risultato.

- (3) Se R = 1, i due numeri sono mutuamente primi e l'algoritmo termina con Z = 1 come risultato; altrimenti, la coppia di valori (X,Y) viene sostituita dalla coppia (Y,R), e si torna al passo (1).

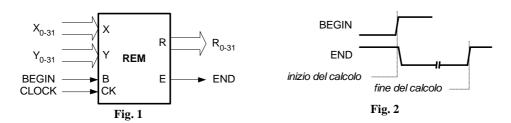

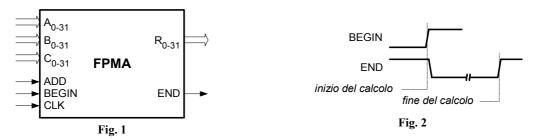

Il calcolo della funzione R = REM(X,Y) viene realizzato mediante un apposito modulo sequenziale (Fig. 1) in cui l'inizio e il termine delle operazioni sono determinati dai segnali presenti rispettivamente all'ingresso BEGIN e all'uscita END (Fig. 2).

Il software di pilotaggio dell'interfaccia è organizzato sotto forma di subroutine che accetta in ingresso un intero N e i puntatori a tre tavole di interi assoluti a 32 bit  $X_i$ ,  $Y_i$ ,  $Z_i$ , con  $0 \le i < N$ . Dopo aver determinato  $Z_i = GCD(X_i, Y_i)$  per ciascun valore di i, la subroutine restituisce anche il numero di coppie  $(X_i, Y_i)$  mutuamente prime trovate nel corso dell'esecuzione.

Progettare l'hardware dell'interfaccia e codificare la relativa subroutine di pilotaggio, corredandola di adeguati commenti.

| 22 |

|----|

|    |

|    |

|    |

|    |

|    |

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

Discussione e verbalizzazione: Lunedì 25 luglio 2005, ore 09:00, Aula 5 (Via del Castro Laurenziano).

#### Calcolatori Elettronici II (A-L) Appello del 14 settembre 2005

| Cognome: |            | Nome: |  |

|----------|------------|-------|--|

|          | Matricola: |       |  |

#### Prima prova (15 punti)

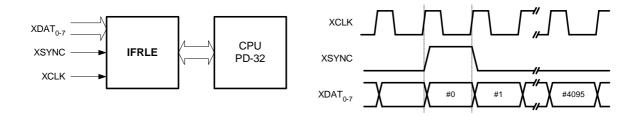

Un'interfaccia IFRLE riceve in continuazione da un bus esterno XDAT<sub>0-7</sub> dati paralleli a 8 bit, sincronizzati a un clock esterno XCLK e a un segnale XSYNC che individua l'inizio di un blocco di 4096 dati.

L'interfaccia comprime il blocco con un algoritmo di *run-length encoding* in cui una sequenza di N byte uguali consecutivi di valore X viene trasformata nella coppia di byte  $\{X, N\}$ ; se N > 255, la sequenza viene suddivisa nel minimo numero di sottosequenze di lunghezza inferiore a 256, ciascuna codificata come sopra. Ad esempio, la sequenza  $\{23\ 23\ 23\ 23\ 23\ 23\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 255\ 37\ 25$

Il software di controllo su CPU PD-32 è organizzato sotto forma di subroutine che:

- accetta come argomenti il puntatore a un buffer e la sua lunghezza;

- avvia la compressione di un blocco di dati;

- acquisisce i risultati della compressione e li dispone ordinatamente nel buffer;

- restituisce al chiamante il numero totale di byte scritti nel buffer, oppure il valore 0 se la dimensione del buffer è insufficiente a contenere i risultati della compressione.

Progettare l'hardware dell'interfaccia e codificare la relativa subroutine di pilotaggio, corredandola di adeguati commenti.

| Firma leggibile |  |

|-----------------|--|

| <br>            |  |

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

Discussione e verbalizzazione: Mercoledì 21 settembre 2005, ore 09:00, Aula 7 (Via del Castro Laurenziano).

#### Calcolatori Elettronici II (A-L) Appello del 16 dicembre 2005

| Cognome: |            | Nome: |  |

|----------|------------|-------|--|

|          | Matricola: |       |  |

#### Prima prova (15 punti)

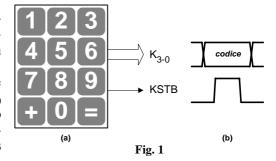

Un'interfaccia IFSUM comprende:

- un modulo di tastiera (Fig. 1a) che, alla pressione di un tasto, genera un codice a 4 bit **K**<sub>3-0</sub> corrispondente al carattere impresso sul tasto e un impulso di validazione **KSTB** (Fig. 1b);

- un modulo di display a 12 caratteri (Fig. 2a) che accetta in ingresso un codice di posizione  $\mathbf{DP}_{3-0}$  (il carattere più a sinistra ha posizione 0, quello più a destra ha posizione 11), un codice di carattere  $\mathbf{DD}_{3-0}$  e un impulso di validazione  $\mathbf{DSTB}$  (Fig. 2b); l'attivazione di  $\mathbf{DSTB}$  produce la visualizzazione del carattere dato nella posizione specificata.

I codici utilizzati sono i normali codici BCD per i caratteri numerici, più le combinazioni **1010** per il simbolo + e **1011** per il simbolo =; la combinazione **1111** viene inoltre accettata dal display come codice di cancellazione.

L'utente imposta due o più operandi numerici separati dal segno + e conclude l'operazione premendo il tasto =; l'interfaccia IFSUM trasmette le informazioni relative alla CPU PD-32, la quale, oltre a presentare sul display i caratteri quando vengono impostati su tastiera, esegue le operazioni di somma richieste e visualizza il risultato sul display. Se il risultato supera le 12 cifre, vengono presentati 12 simboli +.

Progettare l'hardware per l'interfacciamento dei moduli al bus della CPU e codificare il relativo software di pilotaggio, corredandolo di adeguati commenti.

- Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

- Scrivere chiaramente e in maniera ordinata e leggibile.

- Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

- Tempo a disposizione: 2 ore.

- Discussione e verbalizzazione: Martedì 20 dicembre 2005, ore 09:00, Aula 5 (Via del Castro Laurenziano).

| • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | <br>••••• |  |

|-----------------------------------------|-----------------------------------------|-----------|--|

### Calcolatori Elettronici II (A-L) Esonero del 19 giugno 2006

| Cognome: |            | Nome: |  |

|----------|------------|-------|--|

|          | Matricola: |       |  |

### Prova unica (15 punti)

Un'interfaccia IFRNG riceve in continuazione da un bus externo XDATA<sub>0-15</sub> dati paralleli a 16 bit, da interpretare come valori numerici assoluti, sincronizzati a un clock esterno XCLK. La CPU PD-32, dopo aver inviato all'interfaccia due valori numerici M ed N, comanda l'acquisizione di un blocco di 4096 dati consecutivi  $x_i$  ( $0 \le i < 4096$ ) dalle linee XDATA; l'interfaccia genera tre valori numerici P, Q, R tali che:

- P è il conteggio dei valori  $x_i$  tali che  $x_i < M$ ;

- Q è il conteggio dei valori  $x_i$  tali che  $M \le x_i \le N$ ;

- R è il conteggio dei valori  $x_i$  tali che  $N < x_i$ .

I tre risultati P, Q, R vengono quindi trasmessi alla CPU, che li dispone ordinatamente in una tavola RTABLE residente in memoria.

Progettare l'hardware dell'interfaccia IFRNG e codificare il relativo software di pilotaggio sotto forma di subroutine, corredandolo di adeguati commenti.

| <br> | <br> |

|------|------|

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 1.5 ore.

### Calcolatori Elettronici II (A-L) Appello del 6 luglio 2006

| Cognome: |            | <br> |  |

|----------|------------|------|--|

|          | Matricola: | <br> |  |

#### Prima prova (15 punti)

Un'interfaccia IFCMP opera come *coprocessore* per l'esecuzione di moltiplicazioni tra numeri complessi, rappresentati come coppie ordinate di numeri reali floating-point a 32 bit. L'interfaccia riceve dalla CPU PD-32 due operandi complessi  $X = X_R + jX_I$ ,  $Y = Y_R + jY_I$ , dove  $j = \sqrt{-1}$  è l'unità immaginaria, e trasmette alla CPU il risultato

$$Z = Z_R + jZ_I = (X_R Y_R - X_I Y_I) + j(X_R Y_I + X_I Y_R)$$

L'hardware dell'interfaccia utilizza **un singolo** modulo sequenziale FPMA (*Floating-Point Multiply/Add*, Fig. 1) per l'esecuzione dell'operazione  $R = A \pm BC$ , dove A, B, C, R sono numeri **reali** floating-point a 32 bit; oltre alla moltiplicazione, il modulo esegue una somma o una sottrazione a seconda che il suo ingresso ADD sia attivo o meno; l'inizio e il termine delle operazioni del modulo sono determinati dai segnali presenti rispettivamente all'ingresso BEGIN e all'uscita END (Fig. 2).

Il software di pilotaggio è organizzato sotto forma di subroutine che riceve in ingresso:

- un intero N > 0;

- i puntatori a due tavole XTABLE, YTABLE, che contengono rispettivamente N numeri complessi X[i] ed N numeri complessi Y[i];

- il puntatore a una tavola ZTABLE nella quale, dopo l'esecuzione dei calcoli necessari, dovranno essere immagazzinati gli N risultati  $Z[i] = X[i] \cdot Y[i]$ .

Progettare l'hardware dell'interfaccia e codificare la relativa subroutine di pilotaggio, corredando-la di adeguati commenti.

#### NOTE:

- 1. Il modulo FPMA **non** deve essere progettato.

- 2. Il valore 0, qualora necessario, è rappresentato in floating-point come 32 bit tutti uguali a zero.

- Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

- Scrivere chiaramente e in maniera ordinata e leggibile.

- Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

- Tempo a disposizione: 2 ore.

- Discussione e verbalizzazione: Giovedì 13 luglio 2006, ore 09:00, Aula 1 (Via del Castro Laurenziano).

#### Calcolatori Elettronici II (A-L) Appello del 15 luglio 2006

| Cognome: |            | Nome: |  |

|----------|------------|-------|--|

|          | Matricola: |       |  |

#### Prima prova (15 punti)

Un'interfaccia IFSEQ riceve in continuazione dall'esterno dati seriali attraverso una linea XDAT e un clock XCLK (Fig. 1).

Su comando della CPU PD-32, l'interfaccia avvia l'acquisizione di una stringa binaria *S* costituita da 1024 bit consecutivi prelevati dalla linea XDAT; al termine, l'interfaccia trasmette alla CPU i seguenti dati:

- il numero di bit *P* della più lunga sottosequenza di *S* tutta costituita da 0;

- il numero di bit Q della più lunga sottosequenza di S tutta costituita da 1.

Il software di controllo dell'interfaccia, organizzato come subroutine, avvia una singola acquisizione al termine della quale utilizza i valori restituiti dall'interfaccia per aggiornare due tavole PTABLE e QTABLE definite come segue:

- PTABLE[i] contiene il numero di acquisizioni che hanno restituito P = i;

- QTABLE[k] contiene il numero di acquisizioni che hanno restituito Q = k.

Progettare l'hardware dell'interfaccia IFSEQ e codificare il relativo software di controllo, corredandolo di adeguati commenti.

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Giovedì 20 luglio 2006, ore 09:00, Aula 1 (Via del Castro Laurenziano).

#### Calcolatori Elettronici II (A-L) Appello del 14 settembre 2006

| Cognome: |            | Nome: |  |

|----------|------------|-------|--|

|          | Matricola: |       |  |

#### Prima prova (15 punti)

Un'interfaccia IFMVP opera come *coprocessore* per il calcolo di prodotti matrice-vettore  $\mathbf{y} = \mathbf{M}\mathbf{x}$ , dove  $\mathbf{x} = \{x_i, 0 \le i < 4\}$  e  $\mathbf{y} = \{y_i, 0 \le i < 4\}$  sono vettori a 4 componenti e  $\mathbf{M} = \{M_{ij}, 0 \le i, j < 4\}$  è una matrice 4×4; sia le componenti dei vettori che gli elementi della matrice sono numeri floating-point a 64 bit. L'interfaccia riceve dalla CPU PD-32 un vettore  $\mathbf{x}$  e un intero k che identifica una tra 256 matrici  $\mathbf{M}$  immagazzinate in una ROM residente sulla stessa interfaccia, e restituisce alla CPU il vettore prodotto  $\mathbf{y}$  tale che

$$y_i = \sum_{j=0}^{3} M_{ij} x_j$$

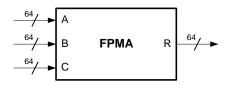

Per l'esecuzione dei calcoli relativi, l'interfaccia utilizza **un singolo** modulo FPMA (*Floating-Point Multiply Add*, Fig. 1) per l'esecuzione dell'operazione R = A + BC, dove A, B, C, R sono numeri reali floating-point a 64 bit; tale operazione viene completata in un tempo non superiore a 4 periodi di System Clock.

Fig. 1

Il software di pilotaggio è organizzato sotto forma di subroutine che riceve in ingresso:

- un intero  $\bar{N} > 0$

- i puntatori a due tavole **KTABLE**, **XTABLE** che contengono rispettivamente *N* interi *k* identificatori di matrice e *N* vettori **x**;

- il puntatore a una tavola **YTABLE** nella quale, dopo l'esecuzione dei calcoli necessari, dovranno essere immagazzinati gli *N* vettori **v** risultanti.

Progettare l'hardware dell'interfaccia e codificare la subroutine di pilotaggio, corredandola di adeguati commenti.

Ai sensi della legge n. 675 del 31/12/96, il/la sottoscritto/a autorizza la pubblicazione su web dei risultati della presente prova.

Firma leggibile

.....

<sup>•</sup> Utilizzare questo foglio come cartellina per contenere i fogli con le risposte.

<sup>•</sup> Scrivere chiaramente e in maniera ordinata e leggibile.

<sup>•</sup> Non è consentito consultare libri o appunti, ed è severamente proibito copiare.

<sup>•</sup> Tempo a disposizione: 2 ore.

<sup>•</sup> Discussione e verbalizzazione: Mercoledì 20 settembre 2006, ore 09:00, Aula 1 (Via Castro Laurenziano).